|

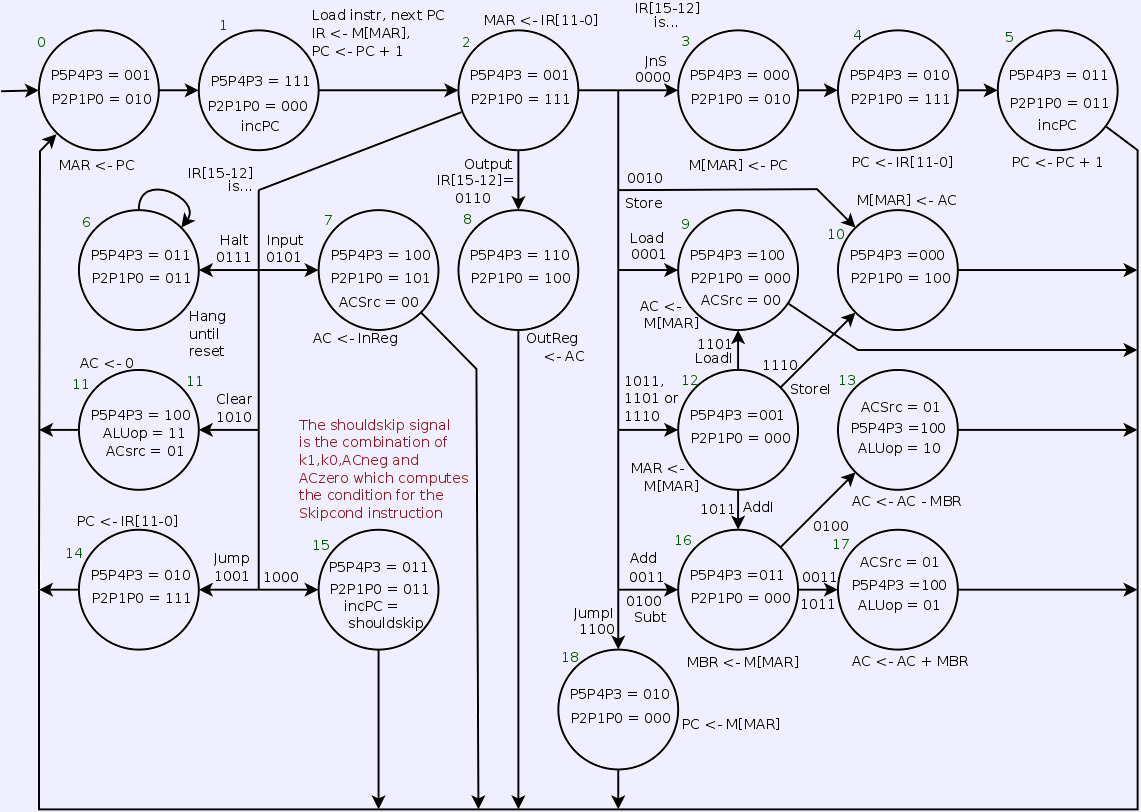

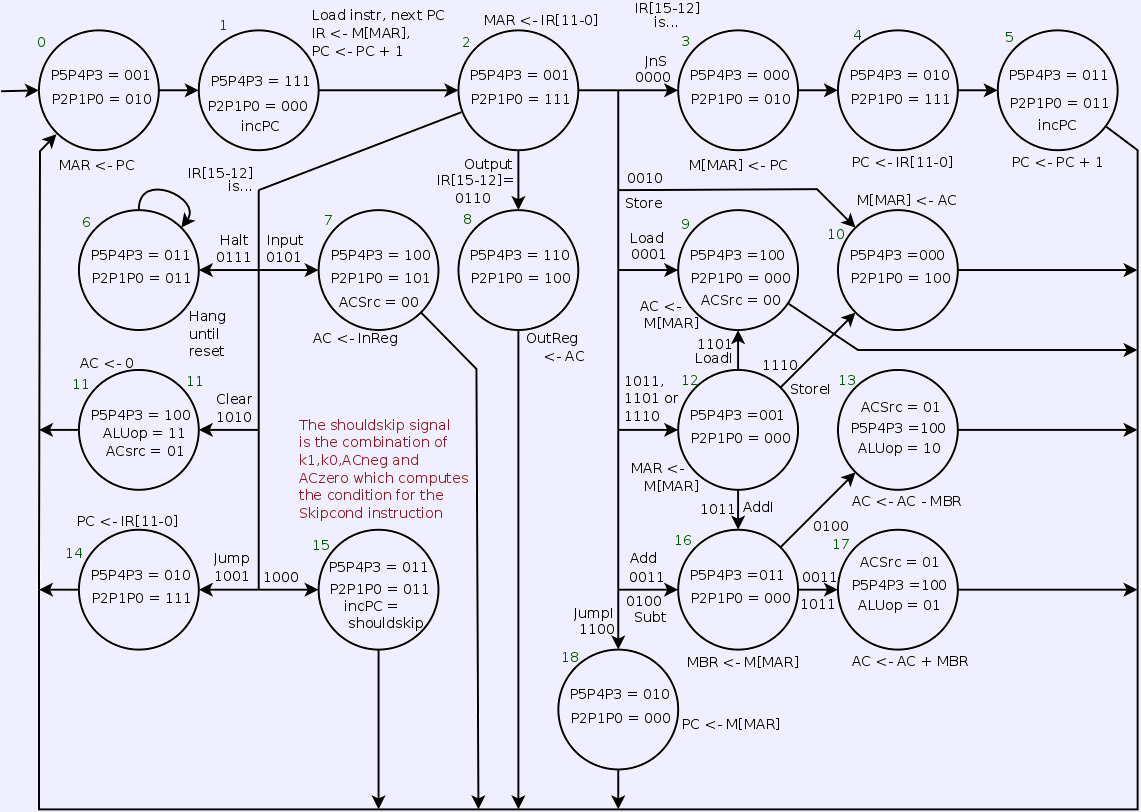

JnS X

[changed]

M[MAR] ← PC

PC ← X

PC ← PC + 1 Load X

[changed]

MAR ← X

AC ← M[MAR] Store X

[changed]

MAR ← X,

M[MAR] ← AC Add X

MAR ← X

MBR ← M[MAR]

AC ← AC + MBR Subt X

MAR ← X

MBR ← M[MAR]

AC ← AC - MBR Input

AC ← InREG Output

OutREG ← AC |

Skipcond

If IR[11-10] = 00 then

If AC < 0 then PC ← PC + 1

else if IR[11-10] = 01 then

If AC = 0 then PC ← PC + 1

else if IR[11-10] = 10 then

If AC > 0 then PC ← PC + 1 Jump X

PC ← IR[11-0] Clear

AC ← 0 AddI X

[changed]

MAR ← X

MAR ← M[MAR]

MBR ← M[MAR]

AC ← AC + MBR JumpI X

[changed]

MAR ← X

PC ← M[MAR] LoadI X

[changed]

MAR ← X

MAR ← M[MAR]

AC ← M[MAR] StoreI X

[changed]

MAR ← X

MAR ← M[MAR]

M[MAR] ← AC |